The International Conference for High Performance Computing, Networking, Storage and Analysis

© computer society

sîghpc

**Sponsors**

# Table of Contents

| Welcome from the Chair2                   |

|-------------------------------------------|

| General Information4                      |

| Registration and Conference Store Hours 4 |

| Exhibit Hall Hours4                       |

| SC16 Information Booth/Hours4             |

| SC17 Preview Booth/Hours4                 |

| Social Events5                            |

| Registration Pass Access                  |

| SCinet 8                                  |

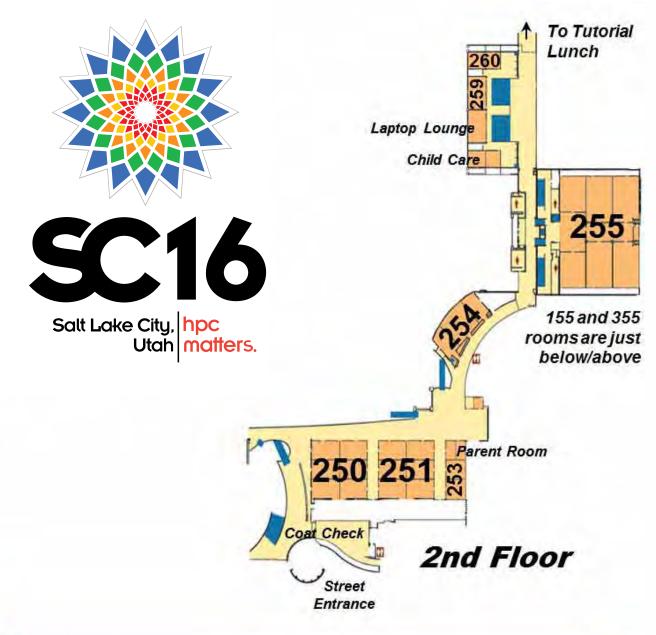

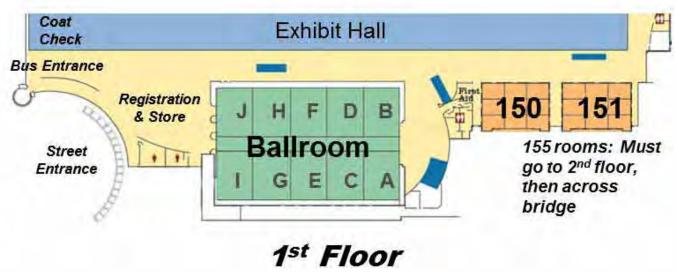

| Convention Center Maps12                  |

| Daily Schedules 14                        |

| Plenary/Keynote/Invited Talks Plenary     |

| Awards Presentations34                    |

| Birds of a Feather37                      |

| Doctoral Showcase50                       |

| Emerging Technologies54                   |

| Exhibitor Forums58                        |

| HPC Impact Showcase66                     |

| Panels                                               | 69  |

|------------------------------------------------------|-----|

| Papers                                               | 73  |

| Posters                                              |     |

| Posters                                              | 98  |

| Research Posters                                     | 105 |

| ACM Student Research Competition                     |     |

| Scientific Visualization/<br>Data Analytics Showcase | 135 |

| Student Programs                                     | 136 |

| Experiencing HPC for Undergraduates                  | 137 |

| Mentor-Protégé Program                               | 137 |

| Student Cluster Competition Kickoff                  | 137 |

| Student-Postdoc Job &                                |     |

| Opportunity Fair                                     | 138 |

| Tutorials                                            | 139 |

| Workshops                                            | 154 |

| Acknowledgements                                     | 168 |

# Welcome to Salt Lake City

Welcome to Salt Lake City for SC16, the international conference for high performance computing, networking, storage and analysis. The city on the shores of the Great Salt Lake offers attendees the best of two worlds: a vibrant metropolis that is one of the fastest growing tech centers in the United States, and the adjacent Wasatch Mountains — a range offering a spectacular backdrop to this glittering jewel.

We're delighted to return to the Salt Palace Convention Center, site of SC12. There's no better place to see why high performance computing matters to our daily lives, our future, our communities and our world. For five days, SC16 will be a global high performance computing hub powered by one of the fastest networks on the planet.

SC provides a unique opportunity to study a complete picture of the state of the art in HPC today and to capture a glimpse into where our community is headed tomorrow. From providing clean water and sanitation to underdeveloped areas of the world and helping coastal cities save lives by better preparing for hurricanes, to developing new drugs for people with early onset Alzheimer's and designing helmets that better protect children and athletes, HPC is powering revolutionary advances that improve our quality of life.

In that vein, keynote speaker Katharine Frase will provide plenty of food for thought in her feature presentation, "Cognitive Computing: How Can We Accelerate Human Decision Making, Creativity and Innovation Using Techniques from Watson and Beyond." http://sc16.supercomputing.org/2016/08/02/sc16-selects-industry-veteran-katharine-frase-keynote-speaker/ Other invited speakers, who also are thought leaders in their fields, will deliver presentations on current topics ranging from the development of new supercomputing capabilities to creating a richer and more diverse HPC workforce.

As in other computing fields, women and other minorities are significantly under-represented in supercomputing, and changing this is vital to ensuring the vitality of the HPC community. Dr. Maria Klawe, president of Harvey Mudd College, will discuss successful strategies for increasing the number of women and students of color in supercomputing in a presentation entitled, "Diversity and Inclusion in Supercomputing." http://sc16.supercomputing.org/2016/09/06/sc16-invited-talk-spotlight-dr-maria-klawe-presents-diversity-inclusion-supercomputing/

SC's own commitment to a diverse workforce and attract young professionals to our field goes back many years, and is anchored by programs such as the Student Cluster Competition, Student Volunteers, the Mentor–Protégé program and the Student Job Fair. Additionally, SC supports members of the HPC community just starting their computing careers through the Early Career Program, which provides an opportunity for special sessions of interest to early career researchers, including getting funding, publishing venues, establishing long-term mentor relationships, and time management.

We are also very excited to add a new facet to these efforts: to better accommodate those with family obligations, SC is offering onsite childcare at the conference for children 6 months to 12 years old. There's no reason SC shouldn't be a family affair! For more information, see http://sc16.supercomputing.org/attendees/on-site-child-care/

The technical program at the heart of the SC is internationally recognized for its breadth and depth, and brings together scientists, engineers, programmers, researchers, system developers and administrators who are leaders in their disciplines. SC's Technical Program is highly competitive and one of the broadest of any HPC conference. SC16 will offer one of the most comprehensive technical programs to date, including presentations, topical panel discussions, papers, tutorials, timely research posters, and Birds-of-a-Feather sessions.

The depth and breadth of topics covered by technical papers has evolved with the conference over the years and selecting those that meet SC's high standard has correspondingly become more difficult. This year, papers cover nine focus areas: Applications; Algorithms; Architectures and Networks; Clouds and Distributed Computing; Data Analytics, Visualization and Storage; Performance Measurement, Modeling and Tools; Programming Systems; State of the Practice; and System Software. Out of 442 technical papers submitted to SC16, only 81 were accepted and of these, seven have been selected as finalists for the conference's Best Paper Award. Reflecting the caliber of talent submitting papers, one of the 'best paper' candidates also is an ACM Gordon Bell Prize finalist.

Popular Technical Program offerings include the panel discussions covering topics of current interest to the HPC community. SC Panels don't just showcase panelists' expertise; they enable participants to engage with key thinkers and producers as more than listeners. Panelists engage in lively, rapid-fire exchanges, often using real-time audience polling, video feeds, and social media to help make panels not only rich with insight, but great fun. The emphasis at SC is on enabling the exchange of ideas through participation and interaction.

Attendees also will have the opportunity to interact with the future of HPC in the Salt Palace's 515,000 sq.ft. exhibition hall, which will feature the latest technologies and accomplishments from the world's leading vendors, research organizations and universities. SC16 will be the first opportunity to learn about many of the technologies that will shape the future of large-scale technical computing and data-driven science.

Innovation is what drives HPC and SC. It is what empowers our community to push the frontiers of science and engineering. A goal of the conference is to serve as a vehicle for advancing the state-of-the-art and broadening the use of HPC by demonstrating how "HPC Matters." SC16 marks the beginning of a multi-year emphasis on advancing our community's 'state-of-the-practice.' A new program track will include all aspects related to the practical use of HPC, including infrastructure, services, facilities, and large-scale application executions. The state-of-the-practice track will include special sessions, papers, panels, workshops, and tutorials that develop and share best practices. Submissions are encouraged from all areas of practice (e.g., system and center determination).

The richness of the conference – with all the opportunities it offers to learn, exchange ideas, and network – can be overwhelming and challenging to navigate, especially to first time attendees. If this is your first SC, welcome! Please take advantage of the resources we've developed especially for you http://sc16.supercomputing. org/attendees/first-time-attendees/. And don't hesitate to stop by one of the information booths or consult our volunteers if you need direction or have questions. We want this to be just the first of many productive years for you at SC.

John West

**SC16 General Chair**

## **General Information**

### **Registration and Conference Store**

The registration area and conference store are located in the South Foyer, Lower Concourse. They will be open during the following days and hours:

| Saturday, November 12  | 1pm – 6pm    |

|------------------------|--------------|

| Sunday, November 13    | 7am – 6pm    |

| Monday, November 14    | 7am – 9pm    |

| Tuesday, November 15   | 7:30am – 6pm |

| Wednesday, November 16 | 7:30am – 6pm |

| Thursday, November 17  | 7:30am – 5pm |

| Friday, November 18    | 8am – 11am   |

#### **Registration Pass Access**

See page 7.

#### **Exhibition Hall Hours**

| Tuesday, November 15   | 10am-6pm |

|------------------------|----------|

| Wednesday, November 16 | 10am-6pm |

| Thursday, November 17  | 10am-3pm |

#### **SC16 Information Booths**

Need up-to-the-minute information about what's happening at the conference. Need to know where to find your next session? What restaurants are close by? Where to get a document printed? These questions and more can be answered by a quick stop at one of the SC Information booths. There are two booth locations for your convenience: the Main Booth is on the Lower Concourse, South Foyer, just near registration and the conference store; the Satellite Booth is located on the Upper Concourse Lobby near Room 251.

#### **SC16 Information Booth Hours**

| Dates              | Main Booth     | Satellite Booth |

|--------------------|----------------|-----------------|

| Saturday, Nov. 12  | 1pm-5pm        | Closed          |

| Sunday, Nov. 13    | 8am-6pm        | 8am-5pm         |

| Monday, Nov. 14    | 8am-7pm        | 8am-5pm         |

| Tuesday, Nov. 15   | 8am-6pm        | 10am-5pm        |

| Wednesday, Nov. 16 | 8am-6pm        | 8am-4pm         |

| Thursday, Nov. 17  | 8am-6pm        | Closed          |

| Friday, Nov. 18    | 8:30am-12:30pm | Closed          |

#### **SC17 Preview Booth**

Members of next year's SC committee will be available in the SC17 preview booth (located in the South Foyer of the convention center) to offer information and discuss next year's SC conference in Denver, Colorado. Stop by for a copy of next year's Call for Participation and pick up some free gifts!

The booth will be open during the following hours:

| Tuesday, November 15   | 10am-3pm |  |

|------------------------|----------|--|

| Wednesday, November 16 | 10am-3pm |  |

| Thursday, November 17  | 10am-3pm |  |

#### **Transportation**

There are many hotels within walking distance of the Convention Center as well as hotels serviced by the light rail service. Additionally, SC16 will provide four bus loops providing transportation from the farther hotels to the Convention Center. The following table provides information on the transportation recommendation for each of the conference hotels.

| Hotel                                           | Transportation Method         |

|-------------------------------------------------|-------------------------------|

| Comfort Inn Salt Lake City Airport              | SC16 Bus: Route #3            |

| Courtyard by Marriott                           | SC16 Bus: Route #2            |

| Courtyard Salt Lake City Downtown               | Walk                          |

| Crystal Inn Salt Lake City Downtown             | SC16 Bus: Route #1            |

| Doubletree Suites by Hilton                     | SC16 Bus: Route #1            |

| Doubletree by Hilton Salt Lake City Airport     | SC16 Bus: Route #3            |

| Fairfield Inn & Suites Salt Lake City           | SC16 Bus: Route #2            |

| Grand America Hotel & Towers                    | Light Rail –                  |

|                                                 | Courthouse Station            |

| Hampton Inn Downtown                            | SC16 Bus: Route #1            |

| Hampton Inn & Suites Salt Lake City Airport     | SC16 Bus: Route #3            |

| Hilton Salt Lake City Center                    | Walk                          |

| Holiday Inn Salt Lake City – Airport West       | SC16 Bus: Route #3            |

| Holiday Inn Express Salt Lake City Downtown     | Walk                          |

| Homewood Suites                                 | SC16 Bus: Route #2            |

| Hotel Monaco                                    | Walk                          |

| Hyatt House Salt Lake City Downtown             | Light Rail –                  |

|                                                 | Arena Station                 |

| Hyatt Place Salt Lake City Airport              | SC16 Bus: Route #3            |

| Hyatt Place Salt Lake City Downtown             | Light Rail –                  |

|                                                 | Arena Station                 |

| La Quinta Inn and Suites Salt Lake City Airport | SC16 Bus: Route #3            |

| Little America                                  | Light Rail Courthouse Station |

| Peery Hotel                                     | Walk                          |

| Radisson Hotel Salt Lake City Downtown          | Walk                          |

| Red Lion Hotel Salt Lake City Downtown          | SC16 Bus: Route #1            |

| Residence Inn City Center                       | SC16 Bus: Route #2            |

| Salt Lake City Marriott Downtown                | Walk                          |

| Salt Lake City Marriott City Center             | Walk                          |

| Salt Lake City Marriott University Park         | SC16 Bus: Route #4            |

| Salt Lake Plaza Hotel                           | Walk                          |

| Sheraton                                        | Light Rail                    |

|                                                 |                               |

#### **SC16 Shuttle Bus Information**

#### **Operational Hours:**

| 1pm- 6pm     |

|--------------|

| 7am- 9pm     |

| 7am- 9pm     |

| 7am- 7:30pm  |

| 7am- 7:30pm  |

| 7am- 9pm     |

| 7am- 12:30pm |

|              |

#### Frequency:

Sunday 11/13 thru Thursday 11/17:

7:00 am - 11:00 am: Buses run approximately every 15-20 minutes 11:00 am - 4:00 pm: Buses run approximately every 30 minutes

Saturday 11/12 and Friday 11/18: Buses will run every approximately every 30 minutes

#### **Social Events**

Exhibitors' Reception (21+ Event)

Sunday, November 13

6pm – 9pm

SKY SLC

149 Pierpont Ave,

Salt Lake City, UT 84101

SC16 will host the Exhibitors' Appreciation Party at SKY SLC, a brief walk from the Convention Center, for registered exhibitors. The Conference would not be what it is without the generous support and enthusiasm of the exhibitors and we look forward to an evening celebrating these partnerships. This year's reception will have an eclectic mix of activities, from cocktails and live music by the Groove Merchants, to local beer sampling and food pairings, to darts and ping-pong. The reception will offer a little something for everyone and lots of fun for all!

An Exhibitor badge, party ticket, and government-issued photo ID are required and you must be 21 or over to attend this event. Each exhibitor will receive two beverage tickets upon arrival to enjoy libations, followed by a cash bar. Complimentary coat check will be provided at the entry to SKY.

Shuttle transportation from the Convention Center back to hotels along the normal bus routes will be available from 6:30pm - 9:30pm.

Exhibits Gala Opening Reception Monday, November 14 7pm-9pm

SC16 will host its annual Grand Opening Gala in the Exhibit Hall. This will be your first opportunity to see the latest high performance computing, networking, storage, analysis, and research products, services, and innovations. This event is open to all Technical Program, Exhibitors and Students@SC registrants.

## Posters Reception Tuesday, November 15 5:15pm-7pm South Foyer & Hall E

The Posters Reception is an opportunity for attendees to interact with poster presenters and includes research and ACM Student Research Competition posters, Doctoral Showcase posters as well as the Scientific Visualization & Data Analytics Showcase. The reception is open to all attendees. Complimentary refreshments and appetizers are available.

Technical Program Conference Reception Thursday, November 17 6pm-9pm The Leonardo

The SC16 conference ensures that the science and innovation at the Conference soar to new heights each year. To thank our Technical Program attendees and to encourage continued interactions, SC16 will host a conference reception for all Technical Program attendees at the Leonardo, an interactive museum now featuring a flight exhibit and additional displays geared to stimulate the mind. With a full-sized C-131 aircraft dangling from the rafters on the ground floor, it would be easy to spend your time at the Reception where you entered, especially if you happen to run into Amelia Earhart or the Wright Brothers. Attendees are encouraged to explore the all three floors of the Museum, as we know you will be pleased with the extensive food, exhibit, and entertainment offerings found throughout the space.

A Tech Program badge, event ticket, and government-issued photo ID are required to attend this event. As the event is open to all ages, please be aware that all attendees over 21 years of age who wish to consume alcoholic beverages must check-in and receive a wristband to receive bar service.

Shuttle transportation to and from the event will run starting at 5:45 pm from the Convention Center. Starting at 7:00 pm, shuttles will provide service from the venue to the standard hotel routes as well as service back to the Convention Center.

#### **Conference Services/Convention Center Facilities**

#### **ATMs**

Two ATM cash machines are located inside the convention center. One is located on the Lower Concourse next to the Parking Garage elevators near the South Lobby. The other is located on the Upper Concourse next to the Business Center and Room 254.

#### **Business Center**

The Salt Palace Business Center is an on-site, full service print, copy and shipping center located inside the convention center on the north end of the upper concourse. For more information, contact the Business Center at 385-468-2228 or businesscenter@saltpalace.com.

The business center will be open from 8:00 a.m. – 5:00 p.m. from Saturday, November 12th through Friday, November 18th.

#### **City and Dining Information**

Stop by the Visit Salt Lake kiosk in the South Foyer of the convention center to discover dining and city options.

| Sunday, November 12    | 10am-6pm |

|------------------------|----------|

| Monday, November 13    | 10am-7pm |

| Tuesday, November 14   | 10am-6pm |

| Wednesday, November 15 | 10am-6pm |

| Thursday, November 16  | 10am-6pm |

#### Coat & Bag Check

There are two coat and bag check stations. One is located near the South Entrance in Exhibit Hall "E" and the other is just inside the East Entrance. The hours for both locations are as follows:

| Saturday, November 12  | Noon-8:00pm |

|------------------------|-------------|

| Sunday, November 13    | 7am-6pm     |

| Monday, November 14    | 7am-10pm    |

| Tuesday, November 15   | 7am-9pm     |

| Wednesday, November 16 | 7am-8pm     |

| Thursday, November 17  | 7am-6pm     |

| Friday, November 18    | 7am-1pm     |

#### **Emergency Contact**

For an onsite emergency, please dial 3040 on any house phone.

#### **Family Day**

Family Day is Wednesday, November 16, 4pm-6pm. Adults and children 12 and over are permitted on the floor during these hours when accompanied by a registered conference attendee.

#### **First-Aid Center**

There are two first aid offices in the convention center. One is on the east side, located next to Room 150A; the other is on the west side lobby, outside of Hall 4.

#### **Lost Badge**

There is a \$40 processing fee to replace a lost badge.

#### **Lost & Found**

Lost and found is located in Room 258.

#### **On-Site Child Care**

#### **Room 257**

On-site childcare services in the convention center is being provided by KiddieCorp for children between ages 6 months through 12 years old. The deadline for sign-up was Friday, October 14, 2016. No drop-in childcare is available. All children using the SC16 childcare services must be registered in advance by a parent or legal guardian. Contact KiddieCorp at 858-455-1718.

#### **Hours:**

| Sunday, November 13th    | 8:00am-6:00pm |

|--------------------------|---------------|

| Monday, November 14th    | 8:00am-9:00pm |

| Tuesday, November 15th   | 8:00am-7:00pm |

| Wednesday, November 16th | 8:00am-7:00pm |

| Thursday, November 17th  | 8:00am-6:00pm |

#### **Parents with Infants Room**

SC16 has provided a lactation room with privacy areas for nursing mothers, located in Room 252A. Each private space will have a plush chair and small table. A sofa with end tables, refrigerator, changing tables, lockers, and diaper disposal will be provided in the common space. The room will be open during the following dates and hours:

| Saturday, November 12  | noon – 5pm |

|------------------------|------------|

| Sunday, November 13    | 8am – 6pm  |

| Monday, November 14    | 8am – 9pm  |

| Tuesday, November 15   | 8am – 9pm  |

| Wednesday, November 16 | 8am – 7pm  |

| Thursday, November 17  | 8am – 6pm  |

| Friday, November 18    | 8am – 1pm  |

#### **Parking**

The Salt Palace Convention Center offers two convenient underground garages that are open 7 days a week:

- South Lot Enter off of 200 South between West Temple and 200 West (600 stalls)

- West Lot Enter off of 300 West between 100 South and South Temple (400 stalls)

- · Handicap parking available in both lots

- Sorry, no in/out privileges or overnight parking; height/length restrictions

- Bicycles racks are located in the garages and in various places outside the facility

- Continuous security surveillance

#### **Prayer & Meditation Room**

The prayer and meditation room is located in Room 260-B and is open Sunday-Thursday, 9am-5pm.

#### Restrooms

Restrooms are located conveniently throughout the convention center, as follows:

#### Lower Level:

- · Halls A-E (located in the back)

- Hall 1

- Halls 4&5 (west side)

- North and South Foyers

- Outside Room 155

#### Upper level:

- Across from 254B and near 255

- Upper Mezzanine (on left-hand side)

#### **Visitor's Center**

The Visitor's Center is located near the East entrance. It is open daily from 9am-5pm.

#### Wheelchair/Scooter Rental

Wheelchairs and medical mobility scooters can be rented from the Salt Palace Business Center. Equipment is located on-site with hourly, daily and event rates.

## **Registration Pass Access**

Each registration category provides access to a different set of conference activities as summarized below.

| Type of                              | Technical | Technical | Tutorials | Worksho | p Exhibitor | Exhibit   |

|--------------------------------------|-----------|-----------|-----------|---------|-------------|-----------|

| Registration                         | Program   | Program   |           | Only    | 24-hour     | Hall Only |

|                                      |           | Workshop  | s         |         | Access      | Tue-Thu   |

| Awards (Thursday/12:45               | *         |           |           |         | *           | *         |

| Birds-of-a-Feather                   | *         |           |           |         | •           | (*)       |

| Conference Reception (Thursday)      |           |           |           |         |             |           |

| Doctoral Showcase                    | *         |           |           |         |             | *         |

| Emerging Technologies                | *         |           | *         | *       | •           | *         |

| Exhibit Floor                        | *         |           |           |         |             | *         |

| Exhibitor Forum                      |           |           |           |         |             | *         |

| Exhibits Gala Opening (Monday)       |           | 4         |           |         | · i         |           |

| <b>Exhibitors Reception</b>          |           |           |           |         | *           |           |

| HPC Impact Showcase                  |           | 2         |           |         | **          | *         |

| HPC Matters Plenary                  |           |           | *         | *       |             | *         |

| Invited Talks (Non-<br>Plenary)      | (8.7      |           |           |         |             |           |

| Invited Talks (Plenary)              | *         | *         |           |         |             |           |

| Keynote (Tuesday)                    | *         |           |           | *       |             | 1         |

| Panels (Tue-Thur)                    |           |           |           |         |             |           |

| Panels (Friday Only)                 |           |           |           |         |             |           |

| Papers                               |           |           |           |         |             |           |

| Posters                              |           | *         |           |         | *           | **        |

| Poster Reception<br>(Tuesday)        |           | •         |           |         |             |           |

| Scientific Visualization<br>Showcase | *         | 9         | 16        |         | •           | *         |

| Tutorial Lunch<br>(Sun/Mon ONLY)     |           |           | *         |         |             |           |

| Tutorial Sessions                    |           |           |           |         |             |           |

| Student Cluster<br>Competition       |           | *         |           |         | *           | *         |

| Workshops                            |           |           |           | *       |             |           |

## Scinet

# The Fastest Network Connecting the Fastest Computers

The Fastest Network Connecting the Fastest Computers SC16 is once again hosting one of the most powerful and advanced networks in the world – SCinet. Created each year for the conference, SCinet brings to life a very high-capacity network that supports the revolutionary applications and experiments that are a hallmark of the SC conference. SCinet will link the convention center to research and commercial networks around the world. In doing so, SCinet serves as the platform for exhibitors to demonstrate the advanced computing resources of their home institutions and elsewhere by supporting a wide variety of bandwidth-driven applications including supercomputing and cloud computing.

Volunteers from academia, government and industry work together to design and deliver the SCinet infrastructure. Industry vendors, service providers and carriers donate millions of dollars in equipment and services needed to build the local and wide area networks. Planning begins more than a year in advance of each SC conference and culminates in a high-intensity installation in the days leading up to the conference.

For SC16, SCinet is exploring up-and-coming topics in the high-performance networking community of SC through the Network Research Exhibition (NRE) and returning for a third year, the INDIS workshop.

In addition, SCinet is continuing its Diversity Program, Women in IT Networking at SC (WINS). It is funded by the NSF and administered by a collaboration between the University Corporation for Atmospheric Research (UCAR), the Department of Energy's Energy Sciences Network (ESnet) and the Keystone Initiative for Network Based Education and Research (KINBER). The ongoing activities center around funding U.S. women in their early to mid-careers to participate in SCinet to get hands-on training and build their professional network. Three alumna of the program are returning to continue their participation, and help mentor the new WINS participants.

# SCinet Network Research Exhibition (NRE)

The NRE is SCinet's forum for displaying new or innovative demonstrations in network testbeds, emerging network hardware, protocols, and advanced network intensive scientific applications that will stretch the boundaries of a high-performance network. This year showcases SCinet's inclusion of Optical Transport Network (OTN) components and Data Center Interconnects (DCI) technologies in the showfloor infrastructure which deliver services to our exhibitors. These technologies allow for increased densities and advanced diagnostic capabilities.

## **SCinet INDIS Workshop**

The third annual INDIS workshop is again part of the Technical Program. Innovating the Network for Data-Intensive Science (INDIS) showcases both demonstrations and technical papers highlighting important developments in high-performance networking. With participants from research, industry, and government, this workshop will discuss topics related to network testbeds, emerging network hardware, protocols, and advanced network-intensive scientific applications.

## **SCinet Collaborators**

SCinet is the result of the hard work and significant contributions of many government, research, education and corporate contributors. Contributors for SC16 include:

## **Platinum**

## Gold

SC16.supercomputing.org SC16 • Salt Lake City, Utah

## **SCinet Collaborators**

## **Silver**

# NOKIA Reservoir Labs

## **SCinet Collaborators**

## **Bronze**

SC16.supercomputing.org SC16 • Salt Lake City, Utah

# Salt Lake Downtown

#### Visit Salt Lake

90 South West Temple, Salt Lake City, Utun 801-534-4900 info@vesitsalilake.com WedSaltLake.com

## RESTAURANTS & BARS

| K   | ESTAUKANTS 8                             | RAK2         |

|-----|------------------------------------------|--------------|

|     | Bambara                                  | 801-363-5454 |

| 0   | Bayleat Bar & Grub                       | 801-359-8490 |

| •   | The Bayou                                | 801-961-8400 |

| 0   | Beehive Tea Room & Wedding Library       | 801-328-4700 |

| 0   | Beerhive Puh                             | 801-364-4268 |

| 0   | Senihana                                 | 801-322-2421 |

| 0   | Blaggi's Ristorante Italiano             | 801-596-7222 |

| 0   | Blue Iguana Restaurant                   | 801-533-8900 |

| 0   | Blue Leman                               | 801-328-2583 |

| •   | Suca di Beppo                            | 801-575-5262 |

| (I) | Cafe SuperNatural                        | 801-363-1000 |

| (D) | Cafe Trang                               | 801-359-1638 |

| (D) | Caffe Molise                             | 801-364-8833 |

| 0   | California Pizza Kitchen                 | 801-456-0075 |

| (D) | Canyon Creek Cafes Food Court            |              |

| 0   | Cedars of Lebanon                        | 801-364-4096 |

| T.  | The Cheesecake Factory                   | 801-532-4706 |

| 0   | Christopher's Seafood & Steakhouse       | 801-519-8515 |

| •   | City Creek Center Food Court             |              |

| Ф   | Clouseau's                               | 801-359-7800 |

| 4   | Club Piastra                             | 801-961-8700 |

| 0   | Copper Bowl Indian Cuisine               | 801-309-7543 |

| 1   | Copper Canyon Grill House & Tavern       | 801-521-7800 |

| 3   | Copper Union                             | 801-355-3282 |

| 4   | Cucina Toscana                           | 801-328-3463 |

| •   | The Bepot                                | 801-456-2800 |

| 0   | Desert Edge Brewery at the Pub           | 801-521-8917 |

| 1   | Destinations                             | 801-531-0800 |

| 0   | Elevations Restaurant                    | 801-537-5019 |

| 0   | Eva                                      | 801-359-8447 |

| 0   | Faustina                                 | 801-746-4441 |

| 0   | 5th Street Grill                         | 801-323-7575 |

| •   | First Press                              | 801-401-2000 |

| 0   | Fleming's<br>Prime Steakhouse & Wine Bar | 801-355-3704 |

| 1   | Frida Bistro                             | 801-983-5692 |

| 0   | The Garden Cate                          | 801-258-5708 |

| (D) | The Garden Restaurant                    | 801-539-3170 |

| 0   | Ginza Japanese Cuisine & Sushi Bar       | 801-322-2224 |

| Φ.  | Gracie's                                 | 801-819-7565 |

| 0   | Grilla Bites                             | 801-456-2425 |

| 0   | Happy Sumo At Gateway                    | 801-456-7866 |

| 1   | Himaliyan Kitchen                        | 801-328-2077 |

| 1   | The Hotel Bar & Nightelub                | 801-487-4310 |

| 0   | Ichiban Sushi & Japanese Guisino         | 801-532-7522 |

| 4   | Iggy's Sports Grill                      | 801-532-9999 |

| d)  | Inferno Cantina                          | 801-883-8838 |

| (D) | JB's Family Restaurant                   | 801-328-8344 |

| 1   | J. Wong's Asian Bistro                   | 801-350-0888 |

| 1   | Keys On Main                             | 801-363-3638 |

| 9   | Kneader's Bakery and Cafe                | 801-428-3051 |

| •   | Kristauf's Martini Bar                   | 801-366-9490 |

| ••       |                                     |              |

|----------|-------------------------------------|--------------|

|          |                                     |              |

| 1        | Lamb's Grill Cafe                   | 801-364-7166 |

| 4        | Legends Pub & Grill                 | 801-355-3598 |

| 3        | The Lion House Pantry Restaurant*   | 801-363-5466 |

| (3)      | Little America Coffee Shop          | 801-596-5700 |

| (3)      | Little America Steak House          | 801-596-5700 |

| 30       | Lumpys Dawntown                     | 801-938-3070 |

| 8        | Market Street Grill - Downtown      | 801-322-4568 |

| 4        | Market Street Oyster Bar - Downtown | 801-531-6044 |

| 0        | Martine                             | 801-363-9328 |

| 1        | Maxwell's East Coast Eatery         | 801-328-0304 |

| 0        | McDonald's                          | 801-364-1614 |

| (3)      | The Melting Pot                     | 801-521-6358 |

| 0        | Murphy's Bar and Grill              | 801-359-7271 |

| 6        | Naked Fish Japanese Bistro          | 801-595-8888 |

| ⊜.       | Nauvoo Cale                         | 801-539-3346 |

| (d)      | New Yorker                          | 801-363-0166 |

| (2)      | Dasis Cafe                          | 801-322-0404 |

|          | Pallet Bistro                       | 801-935-4431 |

| <b>D</b> | P. F. Chang's China Bistro          | 801-539-0500 |

| <b>D</b> | Piastra on Gullivan Plaza           | 801-961-8700 |

| Ø.       | The Plum Restaurant                 | 801-359-7800 |

| 1D       | Poplar Street Pub                   | 801-532-2715 |

| 1        | Raw Bean Coffee House               | 801-990-2326 |

| 1        | The Red Door                        | 801-363-6030 |

| de       | Red Rock Brewing Company L.C.       | 801-521-7446 |

| <b>D</b> | Red's Café                          | 801-521-7373 |

| 1        | Rio Grande Cafe                     | 801-364-3302 |

| <b>D</b> | Rodizio Grill                       | 801-220-0500 |

| 0        | Romano's Macaroni Grill             | 801-521-3133 |

| 0        | The Roof Restaurant                 | 801-539-1911 |

| 0        | Royal Eatery                        | 801-532-4301 |

| (3)      | Ruth's Chris Steak House            | 801-363-2000 |

| (3)      | Sage's Cafe                         | 801-322-3790 |

| (3)      | Salt Lake Roasting Company          | 801-363-7572 |

| 1        | Settebello Pizzeria Napoletana      | 801-322-3556 |

| 1        | Siegfried's Delicatessen, Inc.      | 801-355-3891 |

| of a     | Spencer's For Steaks & Chops        | 801-238-4748 |

| 4        | Squatters Pub Brewery               | 801-363-2739 |

| (3)      | Star of India Restaurant            | 801-363-7555 |

| 0        | Takashi                             | 801-519-9595 |

| 1        | Tayernacle Social Club              | 801-519-8900 |

| (3)      | Texas de Brazil Churrascaria        | 385-232-8070 |

| 0        | The Tin Angal Cafe                  | 801-328-4155 |

| (3)      | Toaster's                           | 801-328-2928 |

| (3)      | Trofi                               | 801-238-4877 |

| 1        | Tucanos Brazilian Grill             | 801-456-2550 |

| 9        | Tucci's Cucina Italiana             | 801-533-9111 |

| 0        | Vinto                               | 801-539-9999 |

| 0        | Vosen's Bread Paradise              | 801-322-2424 |

| -        | Titue Adaminates Reli               | not see name |

Z Tejas Southwestern Grill

TY Restaurant

801-456-0450

801-779-4730

| A   | TRACTIONS                                                 |                 |

|-----|-----------------------------------------------------------|-----------------|

| Ŧ   | Bealtive House                                            | 801-240-2681    |

| 2   | Brewvies Cinema Pub                                       | 801-355-5500    |

| 3   | Brigham Young Historic Park                               |                 |

| 4   | Brigham Young Monument                                    |                 |

| 5   | Broadway Centre Cinemas                                   | 801-321-0310    |

| 6   | Capitol Theatre                                           | 801-355-2787    |

| 7   | Cathedral Church of St. Mark                              | 801-322-3400    |

| 8   | Cathedral of the Madeleine                                | 801-328-8941    |

| 9   | City and County Building                                  | 801-533-0858    |

| 10  | City Creek Center - Movement                              | 801-238-5320    |

| 111 | City Creek Park                                           |                 |

| 12  | Clark Planetarium 💬                                       | 801-456-7827    |

| 13  | Council Hall                                              | 801-538-1900    |

| 34  | Discovery Gateway 🖅                                       | 801-456-5437    |

| 15  | Eagle Gate                                                |                 |

| 16  | EnergySolutions Arena                                     | 801-325-2000    |

| 177 | Family History Library                                    | 801-240-2584    |

| 18  | First Presbyterian Church                                 | 801-363-3889    |

| 18  | Gallivan Center                                           | 801-535-6110    |

| 20  | The Gateway - Socreng Area                                | 801-456-0000    |

| 21  | Historic Trolley Square — Showing Ann                     | 801-521-9877    |

| 72  | Holy Trimity Cathedral<br>Greek Orthodox Church           | 801-328-9581    |

| 75  | Joseph Smith Memorial Building,<br>FamilySearch ** Center | 801-240-1266    |

| 24  | LDS Church Office Building                                | 801-240-2190    |

| 25  | LDS Conference Center                                     | 801-240-0075    |

| 26  | The Leonardo 🚱                                            | 801-531-9800    |

| 27  | Library Square                                            | 801-524-8200    |

| 28  | Lion House 🐨                                              | 801-363-5466    |

| 29  | Maurice Abravanel Hall                                    | 801-355-2787    |

| 10  | Megaplex 12 at the Gateway                                | 801-304-4553    |

| 31  | Memory Grove Park                                         | 801-972-7800    |

| 32  | Mormon Pioneer Memorial Monument                          |                 |

| 33  | Museum of Church History & Art                            | 801-240-3310    |

| M   | The Off Broadway Theatre                                  | 801-355-4628    |

| 35  | Olympic Legacy Plaza                                      | minus 27 Course |

| 36  | Pioneer Memorial Museum                                   | 801-532-6479    |

| 27  | Rio Grande Depot<br>Utah State Historical Society         | 801-533-3500    |

| 38  | Rose Wagner Performing Arts Center                        | 801-323-5800    |

| 39  | Salt Lake Temple                                          |                 |

| 40  | Salt Palace Convention Center                             | 801-534-4777    |

| 41  | Simply Salt Lake Gift Shop                                | 801-534-4906    |

| 42  | Social Hall Heritage Exhibit                              | 801-321-8745    |

| 43  | Tabernacle                                                | 801-240-4872    |

| 11  | Union Pacific Depct                                       |                 |

| 45  | Utah Müseum of Contemporary Art                           | 801-328-4201    |

| 46  | Utah State Capitol                                        | 801-538-3074    |

| 47  | Visitor Information Center                                | 801-534-4900    |

Wisit Salt Lake Connect Pass attractions

## **SATURDAY, NOVEMBER 12**

| Event            | Tine           | Session Title                           | Room           |

|------------------|----------------|-----------------------------------------|----------------|

| Child Care       | 12:00pm-5:00pm | Room for parents with infants           | 252-A          |

| Coat/Bag Check 1 | 12:00pm-8:00pm | Coat and bag check                      | East Entrance  |

| Coat/Bag Check 2 | 12:00pm-8:00pm | Coat and bag check                      | Hall E         |

| Registration     | 1:00pm-6:00pm  | Attendee Registration                   | South Foyer    |

| Store            | 1:00pm-6:00pm  | Conference Store                        | South Foyer    |

| Students@SC      | 5:30pm-7:30pm  | Building Professional Networks Workshop | Exhibit Hall 5 |

## **SUNDAY, NOVEMBER 13**

| Event                | Tine            | Session Title                                               | Room            |

|----------------------|-----------------|-------------------------------------------------------------|-----------------|

| Break                | 10:00am-10:30am | Refreshments (Tutorials/Workshops)                          | 255-Pre+255-A   |

| Break                | 10:00am-10:30am | Refreshments (Tutorials/Workshops)                          | 355-Pre+355-A   |

| Break                | 10:00am-10:30am | Refreshments (Tutorials/Workshops)                          | Hallway 250/251 |

| Break                | 3:00pm-3:30pm   | Refreshments (Tutorials/Workshops)                          | 255-Pre+255-A   |

| Break                | 3:00pm-3:30pm   | Refreshments (Tutorials/Workshops)                          | 355-Pre+355-A   |

| Break                | 3:00pm-3:30pm   | Refreshments (Tutorials/Workshops)                          | Hallway 250/251 |

| Child Care           | 8:00am-6:00pm   | Child care                                                  | 257             |

| Child Care           | 8:00am-6:00pm   | Room for parents with infants                               | 252-A           |

| Coat/Bag Check 1     | 7:00am-6:00pm   | Coat and bag check                                          | East Entrance   |

| Coat/Bag Check 2     | 7:00am-6:00pm   | Coat and bag check                                          | Hall E          |

| Media/Press          | 1:00pm-5:00pm   | Media Room and Press Office                                 | 151-DE          |

| Press Interview Room | 1:00pm-5:00pm   | Interview Room for Press (reservations only)                | 151-F           |

| Reception            | 6:00pm-9:00pm   | Exhibitors' Reception                                       | SKY SLC         |

| Registration         | 7:00am-6:00pm   | Attendee Registration                                       | South Foyer     |

| Store                | 7:00am-6:00pm   | Conference Store                                            | South Foyer     |

| Students@SC          | 8:30am-10:00am  | Diversity & Inclusion: Views from the Field                 | 260             |

| Students@SC          | 10:30am-12:00pm | Panel: Coming out on Behalf of Diversity                    | 260             |

| Students@SC          | 1:30pm-2:15pm   | Education/Career Keynote                                    | 260             |

| Students@SC          | 2:15pm-3:00pm   | Pitch-It Workshop: Learn to Sell Yourself and your Research | 260             |

| Students@SC          | 3:30pm-4:15pm   | Mentoring: Learning from the Pros                           | 260             |

| Students@SC          | 4:15pm-5:00pm   | Life on the Other Side: Early Career Panel                  | 260             |

| Tutorial             | 8:30am-12:00pm  | HPC Acquisition and Commissioning                           | 355-F           |

| Tutorial             | 8:30am-12:00pm  | Solving and Sharing the Puzzle: Modeling and Simulation of  | 250-F           |

|                      |                 | Computer Architectures with SST and OCCAM                   |                 |

| Tutorial             | 8:30am-12:00pm  | Scalable HPC Visualization and Data Analysis Using VisIt    | 255-F           |

|                      |                 |                                                             |                 |

## **SUNDAY, NOVEMBER 13**

| CONDAI, NOVE   |                |                                                                             |                |

|----------------|----------------|-----------------------------------------------------------------------------|----------------|

| Event          | Tine           | Session Title                                                               | Room           |

| Tutorial       | 8:30am-12:00pm | Power-Aware High Performance Computing: Challenges and                      | 255-E          |

|                |                | Opportunities for Application and System Developers                         |                |

| Tutorial       | 8:30am-5:00pm  | Efficient Parallel Debugging for MPI, Threads, and Beyond                   | 250-D          |

| Tutorial       | 8:30am-5:00pm  | Parallel Programming in Modern Fortran                                      | 250-B          |

| Tutorial       | 8:30am-5:00pm  | Productive Programming in Chapel: A Computation-Driven                      | 250-A          |

| Tutorial       | 8:30am-5:00pm  | Introduction  Programming Intel's 2nd Generation Xeon Phi (Knights Landing) | 255 D          |

| Tutorial       | 8:30am-5:00pm  | Parallel I/O In Practice                                                    | 355-В          |

| Tutorial       | 8:30am-5:00pm  | Building the Modern Research Data Portal                                    | 250-C          |

| rutoriat       | 0.30am-3.00pm  | Using the Globus Platform                                                   | 230-0          |

| Tutorial       | 8:30am-5:00pm  | High Performance Python for Scientific Computing                            | 355-E          |

| Tutorial       | 8:30am-5:00pm  | Kokkos: Enabling Manycore Performance Portability for C++                   | 250-E          |

| , 4.5.1.4      | отобрии        | Applications                                                                |                |

| Tutorial       | 8:30am-5:00pm  | Node-Level Performance Engineering                                          | 255-C          |

| Tutorial       | 8:30am-5:00pm  | Parallel Computing 101                                                      | 255-D          |

| Tutorial Lunch | 12:00pm-1:30pm | Tutorial Attendees' Lunch                                                   | Exhibit Hall 5 |

| Tutorial       | 1:30pm-5:00pm  | Insightful Automatic Performance Modeling                                   | 250-F          |

| Tutorial       | 1:30pm-5:00pm  | Essential HPC Finance Practice: Total Cost of Ownership (TCO),              | 355-F          |

|                |                | Internal Funding, and Cost-Recovery Models                                  |                |

| Tutorial       | 1:30pm-5:00pm  | Managing HPC Software Complexity with Spack                                 | 255-F          |

| Tutorial       | 1:30pm-5:00pm  | Big Data Meets HPC: Exploiting HPC Technologies for                         | 355-C          |

|                |                | Technologies for Accelerating Apache Hadoop, Spark, and                     |                |

|                |                | Memcached                                                                   |                |

| Workshop       | 9:00am-12:30pm | WOLFHPC: Sixth International Workshop on Domain-Specific                    | 251-F          |

|                |                | Languages and High-Level Frameworks for HPC                                 |                |

| Workshop       | 9:00am-12:30pm | 3rd International Workshop on HPC User Support Tools                        | 155-E          |

|                |                | (HUST-16)                                                                   |                |

| Workshop       | 9:00am-12:30pm | HPGDMP'16: First International Workshop on High Performance                 | 251-C          |

|                |                | Graph Data Management and Processing                                        |                |

| Workshop       | 9:00am-5:30pm  | IA^3 2016 - 6th Workshop on Irregular                                       | 251-D          |

|                |                | Applications: Architectures and Algorithms                                  |                |

| Workshop       | 9:00am-5:30pm  | ISAV 2016: In Situ Infrastructures for Enabling Extreme-Scale               | 251-A          |

|                |                | Analysis and Visualization                                                  |                |

| Workshop       | 9:00am-5:30pm  | Workshop on Latest Advances in Scalable Algorithms for                      | 251-E          |

|                | 0.00           | Large-Scale Systems                                                         | 455 4          |

| Workshop       | 9:00am-5:30pm  | ExaMPI16                                                                    | 155-A          |

| Workshop       | 9:00am-5:30pm  | Innovating the Network for Data Intensive Science (INDIS 2016)              | 155-F          |

| Workshop       | 9:00am-5:30pm  | Computational Approaches for Cancer                                         | 251-B          |

| Workshop       | 9:00am-5:30pm  | 7th International Workshop on Performance Modeling,                         | 155-B          |

|                |                | Benchmarking & Simulation of HPC Systems (PMBS16)                           |                |

## **SUNDAY, NOVEMBER 13**

| Event    | Tine          | Session Title                                                 | Room  |

|----------|---------------|---------------------------------------------------------------|-------|

| Workshop | 9:00am-5:30pm | Seventh Annual Workshop for the Energy Efficient HPC          | 155-C |

|          |               | Working Group (EE HPC WG)                                     |       |

| Workshop | 9:00am-5:30pm | Women in HPC: Diversifying the HPC Community                  | 355-D |

| Workshop | 2:00pm-5:30pm | Workshop on Extreme-Scale Programming Tools                   | 155-E |

| Workshop | 2:00pm-5:30pm | The Fourth International Workshop on Software Engineering for | 251-C |

|          |               | HPC in Computational Science and Engineering                  |       |

## **MONDAY, NOVEMBER 14**

| Event                | Tine            | Session Title                                     | Room            |

|----------------------|-----------------|---------------------------------------------------|-----------------|

| Break                | 10:00am-10:30am | Refreshments (Tutorials/Workshops)                | 255-Pre+255-A   |

| Break                | 10:00am-10:30am | Refreshments (Tutorials/Workshops)                | 355-Pre+355-A   |

| Break                | 10:00am-10:30am | Refreshments (Tutorials/Workshops)                | Hallway 250/251 |

| Break                | 3:00pm-3:30pm   | Refreshments (Tutorials/Workshops)                | 255-Pre+255-A   |

| Break                | 3:00pm-3:30pm   | Refreshments (Tutorials/Workshops)                | 355-Pre+355-A   |

| Break                | 3:00pm-3:30pm   | Refreshments (Tutorials/Workshops)                | Hallway 250/251 |

| Child Care           | 8:00am-9:00pm   | Child care                                        | 257             |

| Child Care           | 8:00am-9:00pm   | Room for parents with infants                     | 252-A           |

| Coat/Bag Check 1     | 7:00am-10:00pm  | Coat and bag check                                | East Entrance   |

| Coat/Bag Check 2     | 7:00am-10:00pm  | Coat and bag check                                | Hall E          |

| Early Career Program | 8:30am-10:00am  | Introduction & Peer Networking/ Time Management   | 251-D           |

| Early Career Program | 10:00am-10:30am | Morning Break                                     | Hallway 250/251 |

| Early Career Program | 10:30am-12:00pm | Planning Your Career/Career Networking            | 251-D           |

| Early Career Program | 12:00pm-1:30pm  | Lunch (program participants only)                 | Exhibit Hall 5  |

| Early Career Program | 1:30pm-3:00pm   | Funding Your Research/ Publications Venues        | 251-D           |

|                      |                 | & the Review Process                              |                 |

| Early Career Program | 3:00pm-3:30pm   | Afternoon Break                                   | Hallway 250/251 |

| Early Career Program | 3:30pm-5:00pm   | Speed Mentoring                                   | 251-D           |

| Inclusivity          | 4:30pm-5:15pm   | Introduction to SC16 for First Time Attendees     | 260             |

| Media/Press          | 9:00am-5:00pm   | Media Room and Press Office                       | 151-DE          |

| Plenary              | 5:45pm-6:45pm   | HPC Matters Plenary Panel Discussion:             | Ballroom        |

|                      |                 | HPC and Precision Medicine                        |                 |

| Press Briefing       | 12:00pm-1:30pm  | Top500                                            | 151-F           |

| Press Interview Room | 9:00am-5:00pm   | Interview Room for Press (reservations only)      | 151-F           |

| Reception            | 7:00pm-9:00pm   | Gala Opening Reception                            | Exhibit Halls   |

|                      |                 |                                                   | A-E, 1-5        |

| Registration         | 7:00am-9:00pm   | Attendee Registration                             | South Foyer     |

| Store                | 7:00am-9:00pm   | Conference Store                                  | South Foyer     |

| Students@SC          | 8:30am-10:00am  | Finding Your Way: The Possibilities, Pitfalls and | 260             |

|                      |                 | Practice of HPC Research                          |                 |

|                      |                 |                                                   |                 |

## **MONDAY, NOVEMBER 14**

| Event       | Tine            | Session Title                                              | Room           |

|-------------|-----------------|------------------------------------------------------------|----------------|

| Students@SC | 10:30am-12:00pm | How To: Getting Started in the HPC Community               | 260            |

| Students@SC | 1:30pm-3:00pm   | Navigating SC16; Getting Involved with SC17                | 260            |

| Students@SC | 2:00pm-3:00pm   | Experiencing HPC for Undergrades Reception                 | 151-B          |

| Students@SC | 3:00pm-5:00pm   | Experiencing HPC for Undergrades Orientation               | 151-B          |

| Students@SC | 3:30pm-5:00pm   | Mentor-Protégé                                             | Exhibit Hall 5 |

| Students@SC | 7:30pm-9:00pm   | Student Cluster Competition Kickoff                        | Exhibit Hall 1 |

| Tutorial    | 8:30am-12:00pm  | Harnessing the Power of FPGAs with Altera's SDK for OpenCL | 355-F          |

| Tutorial    | 8:30am-12:00pm  | Container Computing for HPC and Scientific Workflows       | 355-B          |

| Tutorial    | 8:30am-12:00pm  | Programming Your GPU with OpenMP: A Hands-On Introduction  | 255-B          |

| Tutorial    | 8:30am-12:00pm  | Secure Coding Practices and Automated Assessment Tools     | 250-C          |

| Tutorial    | 8:30am-12:00pm  | InfiniBand and High-Speed Ethernet for Dummies             | 355-C          |

| Tutorial    | 8:30am-5:00pm   | Advanced MPI Programming                                   | 355-E          |

| Tutorial    | 8:30am-5:00pm   | Hands-On Practical Hybrid Parallel Application             | 250-B          |

|             |                 | Performance Engineering                                    |                |

| Tutorial    | 8:30am-5:00pm   | Large Scale Visualization with ParaView                    | 250-D          |

| Tutorial    | 8:30am-5:00pm   | Debugging and Performance Analysis on Native and Offload   | 250-A          |

|             |                 | HPC Architectures                                          |                |

| Tutorial    | 8:30am-5:00pm   | Application Porting and Optimization on                    | 255-F          |

|             |                 | GPU-Accelerated POWER Architectures                        |                |

| Tutorial    | 8:30am-5:00pm   | How to Analyze the Performance of Parallel Codes 101       | 255-E          |

| Tutorial    | 8:30am-5:00pm   | Linear Algebra Libraries for HPC: Scientific               | 250-E          |

|             |                 | Computing with Multicore and Accelerators                  |                |

| Tutorial    | 8:30am-5:00pm   | Advanced OpenMP: Performance and 4.5 Features              | 255-C          |

| Tutorial    | 8:30am-5:00pm   | Fault-Tolerance for HPC: Theory and Practice               | 250-F          |

| Tutorial    | 12:00pm-1:30pm  | Tutorial Attendees' Lunch                                  | Exhibit Hall 5 |

| Tutorial    | 1:30pm-5:00pm   | InfiniBand and High-Speed Ethernet: Advanced Features,     | 355-C          |

|             |                 | Challenges in Designing HEC Systems, and Usage             |                |

| Tutorial    | 1:30pm-5:00pm   | Data Center Design and Planning for HPC Folks              | 355-F          |

| Tutorial    | 1:30pm-5:00pm   | Testing of HPC Scientific Software                         | 255-B          |

| Tutorial    | 1:30pm-5:00pm   | Vectorization Strategies for Intel's 2nd Generation        | 355-B          |

|             |                 | Intel Xeon® Phi™ Architecture Named Knights Landing        |                |

| Tutorial    | 1:30pm-5:00pm   | Programming Irregular Applications with OpenMP:            | 250-C          |

|             |                 | A Hands-On Introduction                                    |                |

| Workshop    | 9:00am-12:30pm  | MTAGS16: 9th Workshop on Many-Task Computing on Clouds,    | 251-B          |

| ·           | ·               | Grids, and Supercomputers                                  |                |

| Workshop    | 9:00am-12:30pm  | The Seventh International Workshop on Data-Intensive       | 251-E          |

| ·           | •               | Computing in the Cloud                                     |                |

| Workshop    | 9:00am-12:30pm  | Second International Workshop on Heterogeneous             | 251-C          |

|             |                 | Computing with Reconfigurable Logic                        |                |

| Workshop    | 9:00am-12:30pm  | Machine Learning in HPC Environments                       | 355-D          |

## **MONDAY, NOVEMBER 14**

| Event    | Time           | Session Title                                             | Room  |

|----------|----------------|-----------------------------------------------------------|-------|

| Workshop | 9:00am-12:30pm | Third SC Workshop on Best Practices for HPC Training      | 155-F |

| Workshop | 9:00am-5:30pm  | Energy Efficient Supercomputing (E2SC)                    | 255-D |

| Workshop | 9:00am-5:30pm  | Taking Supercomputing to the Clinic:                      | 251-A |

|          |                | Medical Image Analysis and Visualization                  |       |

| Workshop | 9:00am-5:30pm  | Joint International Workshop on Parallel Data Storage and | 155-C |

|          |                | Data Intensive Scalable Computing Systems (PDSW-DISCS)    |       |

| Workshop | 9:00am-5:30pm  | 7th SC Workshop on Big Data Analytics: Challenges         | 155-A |

|          |                | and Opportunities                                         |       |

| Workshop | 9:00am-5:30pm  | LLVM-HPC2016: Third Workshop on the LLVM                  | 251-F |

|          |                | Compiler Infrastructure in HPC                            |       |

| Workshop | 9:00am-5:30pm  | The 1st International Workshop on Post-Moore              | 155-B |

|          |                | Era Supercomputing (PMES)                                 |       |

| Workshop | 9:00am-5:30pm  | PyHPC 2016: 6th Workshop on Python for                    | 155-E |

|          |                | High-Performance and Scientific Computing                 |       |

| Workshop | 2:00pm-5:30pm  | HPC Systems Professional Workshop                         | 155-F |

| Workshop | 2:00pm-5:30pm  | Third International Workshop on Accelerator               | 251-C |

|          |                | Programming Using Directives (WACCPD)                     |       |

| Workshop | 2:00pm-5:30pm  | Workshop on Education for High Performance                | 251-E |

|          |                | Computing (EduHPC)                                        |       |

| Workshop | 2:00pm-5:30pm  | The 11th Workshop on Workflows in Support of              | 355-D |

|          |                | Large-Scale Science                                       |       |

| Workshop | 2:00pm-5:30pm  | PAW: PGAS Applications Workshop                           | 251-B |

## **TUESDAY, NOVEMBER 15**

| Event              | Tine            | Session Title                                                  | Room          |

|--------------------|-----------------|----------------------------------------------------------------|---------------|

| Break              | 10:00am-10:30am | Refreshments (Tech Program)                                    | 255-Pre+255-A |

| Break              | 10:00am-10:30am | Refreshments (Tech Program)                                    | 355-Pre+355-A |

| Break              | 3:00pm-3:30pm   | Refreshments (Tech Program)                                    | 255-Pre+255-A |

| Break              | 3:00pm-3:30pm   | Refreshments (Tech Program)                                    | 355-Pre+355-A |

| Birds of a Feather | 10:30am-12:00pm | Meeting of the SIGHPC - Big Data Chapter                       | 155-A         |

| Birds of a Feather | 12:00pm-1:30pm  | 13th Graph500 List                                             | 155-A         |

| Birds of a Feather | 12:15pm-1:15pm  | SAGE2: Scalable Amplified Group Environment for                | 250-E         |

|                    |                 | Global Collaboration                                           |               |

| Birds of a Feather | 12:15pm-1:15pm  | Burst Buffers: Early Experiences and Outlook                   | 255-D         |

| Birds of a Feather | 12:15pm-1:15pm  | Next Generation of Co-Processors Emerges: In-Network Computing | 255-EF        |

| Birds of a Feather | 12:15pm-1:15pm  | The 2016 HPC Challenge Awards                                  | 155-C         |

| Birds of a Feather | 12:15pm-1:15pm  | Lustre Deployments for the Next 5 Years                        | 255-BC        |

| Birds of a Feather | 12:15pm-1:15pm  | HPC Education: Meeting of the SIGHPC Education Chapter         | 355-D         |

|                    |                 |                                                                |               |

## **TUESDAY, NOVEMBER 15**

| Event                 | Tine            | Session Title                                                                    | Room                      |

|-----------------------|-----------------|----------------------------------------------------------------------------------|---------------------------|

| Birds of a Feather    | 12:15pm-1:15pm  | New Technologies, Platforms and Services for<br>Sharing Research Data            | 250-D                     |

| Birds of a Feather    | 12:15pm-1:15pm  | On-Demand Infrastructure for Data Analytics and Storage                          | 250-C                     |

| Birds of a Feather    | 12:15pm-1:15pm  | SIGHPC Annual Member Meeting                                                     | 355-F                     |

| Birds of a Feather    | 1:30pm-3:00pm   | OpenStack for HPC: Best Practices for Optimizing Software-Defined Infrastructure | 155-A                     |

| Birds of a Feather    | 5:15pm-7:00pm   | Emerging Trends in HPC Systems and Application Modernization                     | 255-D                     |

| Birds of a Feather    | 5:15pm-7:00pm   | OpenMP: Where Is It Now and Where Is It Going?                                   | 355-E                     |

| Birds of a Feather    | 5:15pm-7:00pm   | Reconfigurable Supercomputing                                                    | 250-F                     |

| Birds of a Feather    | 5:15pm-7:00pm   | MPICH: A High-Performance Open-Source MPI Implementation                         | 250-E                     |

| Birds of a Feather    | 3:30pm-5:00pm   | The Future of NSF Advanced Cyberinfrastructure                                   | 155-A                     |

| Birds of a Feather    | 5:15pm-7:00pm   | TOP500 Supercomputers                                                            | 255-EF                    |

| Birds of a Feather    | 5:15pm-7:00pm   | Energy Efficiency Considerations and HPC Procurement                             | 255-BC                    |

| Birds of a Feather    | 5:15pm-7:00pm   | The 2016 Ethernet Roadmap                                                        | 155-C                     |

| Birds of a Feather    | 5:15pm-7:00pm   | Distributed Machine Intelligence Using Tensorflow                                | 155-E                     |

| Birds of a Feather    | 5:15pm-7:00pm   | How to Build Diverse Teams for More Effective Research                           | 250-C                     |

| Birds of a Feather    | 5:15pm-7:00pm   | Today's Hot Technology: The Growing Necessity of Liquid Cooled HPC               | 355-D                     |

| Birds of a Feather    | 5:15pm-7:00pm   | Experimental Infrastructure and Methodology for HPC Cloud Research               | 250-D                     |

| Child Care            | 8:00am-7:00pm   | Child care                                                                       | 257                       |

| Child Care            | 8:00am-9:00pm   | Room for parents with infants                                                    | 252-A                     |

| Coat/Bag Check 1      | 7:00am-9:00pm   | Coat and bag check                                                               | East Entrance             |

| Coat/Bag Check 2      | 7:00am-9:00pm   | Coat and bag check                                                               | Hall E                    |

| Doctoral Showcase     | 10:30am-12:00pm | Doctoral Showcase 1                                                              | 155-C                     |

| Doctoral Showcase     | 1:30pm-3:00pm   | Doctoral Showcase 2                                                              | 155-C                     |

| Doctoral Showcase     | 3:30pm-5:00pm   | Doctoral Showcase 3                                                              | 155-C                     |

| Doctoral Showcase     | 5:15pm-7:00pm   | Poster Presentations                                                             | Exhibit Hall E            |

| Emerging Technologies | 10:00am-6:00pm  | Emerging Technologies Exhibits                                                   | 155-B                     |

| Exhibitor Forum       | 10:30am-12:00pm | Tools                                                                            | 155-E                     |

| Exhibitor Forum       | 10:30am-12:00pm | Burst Buffers & GPUs                                                             | 155-F                     |

| Exhibitor Forum       | 3:30pm-5:00pm   | Networking                                                                       | 155-F                     |

| Exhibitor Forum       | 3:30pm-5:00pm   | Workflow                                                                         | 155-E                     |

| Exhibits              | 10:00am-6:00pm  | Exhibits                                                                         | Exhibit Halls<br>A-E, 1-5 |

| HPC Impact Showcase   | 1:00pm-3:30pm   | HPC Impact Showcase                                                              | 155-E                     |

|                       |                 |                                                                                  |                           |

## **TUESDAY, NOVEMBER 15**

| Event                | Time                             | Session Title                                                                                                                                                                                                                                                                                     | Room                         |

|----------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Invited Talks        | 10:30am-12:00pm                  | <ul> <li>Understanding Cities through Computation,         Data Analytics and Measurement         Charles Catlett (Argonne National Laboratory)     </li> <li>The Materials Project—A Google of Materials         Kristin Persson (Lawrence Berkeley         National Laboratory)     </li> </ul> | Ballroom                     |

| Invited Talks        | 1:30pm-2:30pm                    | Test of Time Award Special Lecture: Automatically Tuned Linear Algebra Software Clint Whaley, Jack Dongarra (University of Tennessee)                                                                                                                                                             | Ballroom                     |

| Keynote              | 8:30am-10:00am                   | Dr. Katharine Frase  Cognitive Computing: How Can We Accelerate  Human Decision Making, Creativity and Innovation  Using Techniques from Watson and Beyond?                                                                                                                                       | Ballroom                     |

| Media/Press          | 8:00am-5:00pm                    | Media Room and Press Office                                                                                                                                                                                                                                                                       | 151-DE                       |

| Panel                | 10:30am-12:00pm                  | Different Architectures, Different Times: Reproducibility and Repeatability in HPC                                                                                                                                                                                                                | 255-BC                       |

| Panel                | 1:30pm-3:00pm                    | National Strategic Computing Initiative Update                                                                                                                                                                                                                                                    | 255-BC                       |

| Panel                | 3:30pm-5:00pm                    | HPC Workforce Development: How Do We Find Them, Recruit Them, and Teach Them to Be Today's Practitioners and Tomorrow's Leaders?                                                                                                                                                                  | 255-BC                       |

| Papers               | 10:30am-12:00pm                  | Systems and Networks I                                                                                                                                                                                                                                                                            | 355-BC                       |

| Papers               | 10:30am-12:00pm                  | Molecular Dynamics Simulation                                                                                                                                                                                                                                                                     | 355-D                        |

| Papers Papers        | 10:30am-12:00pm<br>1:30pm-3:00pm | State-of-the-Practice: Advanced Applications Development Numerical Algorithms I                                                                                                                                                                                                                   | 255-EF<br>355-E              |

| Papers               | 1:30pm-3:00pm                    | Resilience and Error Handling                                                                                                                                                                                                                                                                     | 355-BC                       |